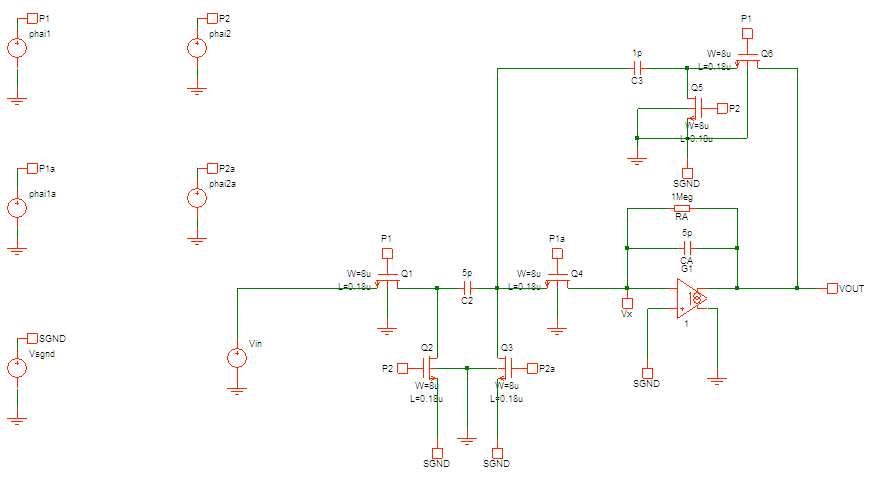

Problem 14.20

1. Offset voltage

1-1. Schematic

1-2. HSPICE Netlist

* Problem 14.20 for dc offset voltage

* MOS model

.include p18_cmos_models_tt.inc

*main circuit (first order switched capacitor filter)

m1 Q1_D P1 Vin_P 0 nmos L=0.18u W=8u

m2 Q1_D P2 SGND 0 nmos L=0.18u W=8u

m3 Q3_D P2a SGND 0 nmos L=0.18u W=8u

m4 Vx P1a Q3_D 0 nmos L=0.18u W=8u

m5 C3_P P2 SGND 0 nmos L=0.18u W=8u

m6 VOUT P1 C3_P 0 nmos L=0.18u W=8u

G1 0 VOUT SGND Vx 1

C2 Q3_D Q1_D 5p

C3 C3_P Q3_D 1p

CA VOUT Vx 5p

RA VOUT Vx 1Meg

** We put RA for convergence.

* voltage source

Vin Vin_P 0 0.9

Vsgnd SGND 0 0.9

* clocks

Vphai1a P1a 0 Pulse(0 1.8 0 10p 10p 390n 1u)

Vphai2a P2a 0 Pulse(0 1.8 500n 10p 10p 390n 1u)

Vphai1 P1 0 Pulse(0 1.8 0 10p 10p 400n 1u)

Vphai2 P2 0 Pulse(0 1.8 500n 10p 10p 400n 1u)

* analysis

.op

.tran 1n 2u

* options

.options post chgtol=1e-16

.end

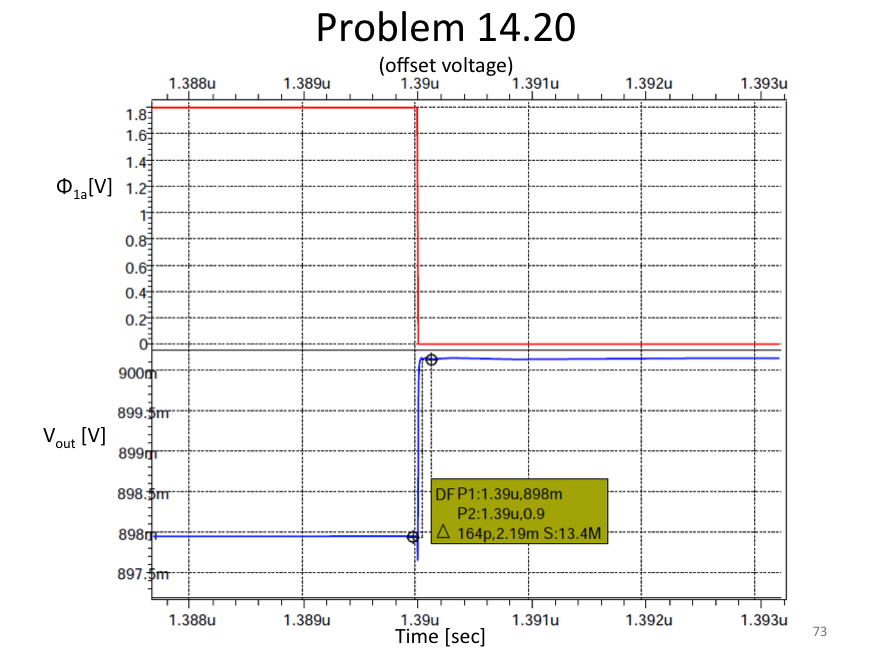

1-3. Simulation Result

Voffset = 2.2mV

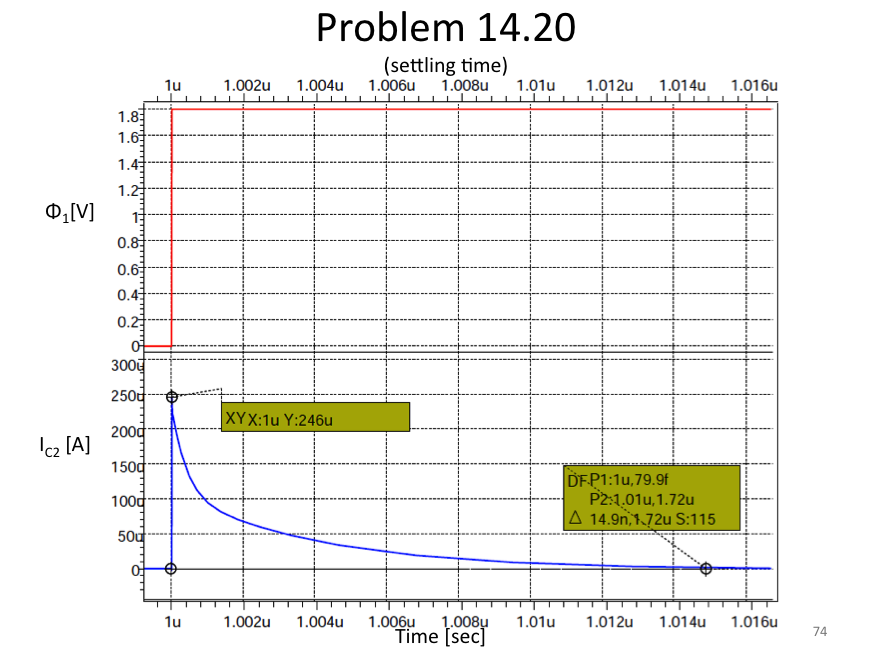

2. Settling time

2-1. Schematic

2-2. HSPICE Netlist

* Problem 14.20 for c2 settling time

* MOS model

.include p18_cmos_models_tt.inc

*main circuit (first order switched capacitor filter)

m1 Q1_D P1 Vin_P 0 nmos L=0.18u W=8u

m2 Q1_D P2 SGND 0 nmos L=0.18u W=8u

m3 Q3_D P2a SGND 0 nmos L=0.18u W=8u

m4 Vx P1a Q3_D 0 nmos L=0.18u W=8u

m5 C3_P P2 SGND 0 nmos L=0.18u W=8u

m6 VOUT P1 C3_P 0 nmos L=0.18u W=8u

G1 0 VOUT SGND Vx 1

C2 Q1_D Q3_D 5p

C3 Q3_D C3_P 1p

CA VOUT Vx 5p

RA VOUT Vx 1Meg

** We put RA for convergence.

* voltage source

Vin Vin_P 0 1.0

Vsgnd SGND 0 0.9

* clocks

Vphai1a P1a 0 Pulse(0 1.8 0 10p 10p 390n 1u)

Vphai2a P2a 0 Pulse(0 1.8 500n 10p 10p 390n 1u)

Vphai1 P1 0 Pulse(0 1.8 0 10p 10p 400n 1u)

Vphai2 P2 0 Pulse(0 1.8 500n 10p 10p 400n 1u)

* analysis

.op

.tran 1p 2u

* options

.options post chgtol=1e-16 method=gear

.print lx1(C2)

.end

2-3. Simulation Result