Example 6.11

1. Unity-gain frequency

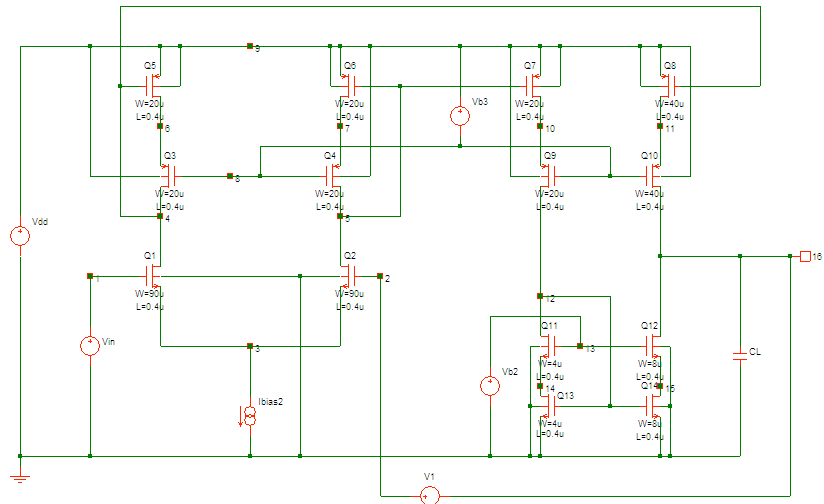

1-1. Schematic

1-2. HSPICE Netlist

* Example 6.11 for unity-gain frequency

* MOS model

.include p18_cmos_models_tt.inc

* main circuit (Current-mirror opamp)

* input stage

m1 4 1 3 0 nmos w=90u l=0.4u

m2 5 2 3 0 nmos w=90u l=0.4u

m3 4 8 6 9 pmos w=40u l=0.4u

m4 5 8 7 9 pmos w=40u l=0.4u

m5 6 4 9 9 pmos w=20u l=0.4u

m6 7 5 9 9 pmos w=20u l=0.4u

*output stage

m7 10 5 9 9 pmos w=20u l=0.4u

m8 11 4 9 9 pmos w=40u l=0.4u

m9 12 8 10 9 pmos w=20u l=0.4u

m10 16 8 11 9 pmos w=40u l=0.4u

m11 12 13 14 0 nmos w=4u l=0.4u

m12 16 13 15 0 nmos w=8u l=0.4u

m13 14 12 0 0 nmos w=4u l=0.4u

m14 15 12 0 0 nmos w=8u l=0.4u

*load capacitance

cl 16 0 2.5p

*cl 16 0 5p

**change cl value for 75 degree phase margin without lead compensation

* current source

Ibias 3 0 160u

* voltage source

Vdd 9 0 1.8

Vin 1 0 1 pulse(750m 1.25 0 1n 1n 49n 100n)

Vb1 13 0 1.4

Vb2 9 8 1.2

V1 2 16 dc=0 ac=1

* analysis

.op

.ac dec 10 1k 100G

* options

.options post

.end

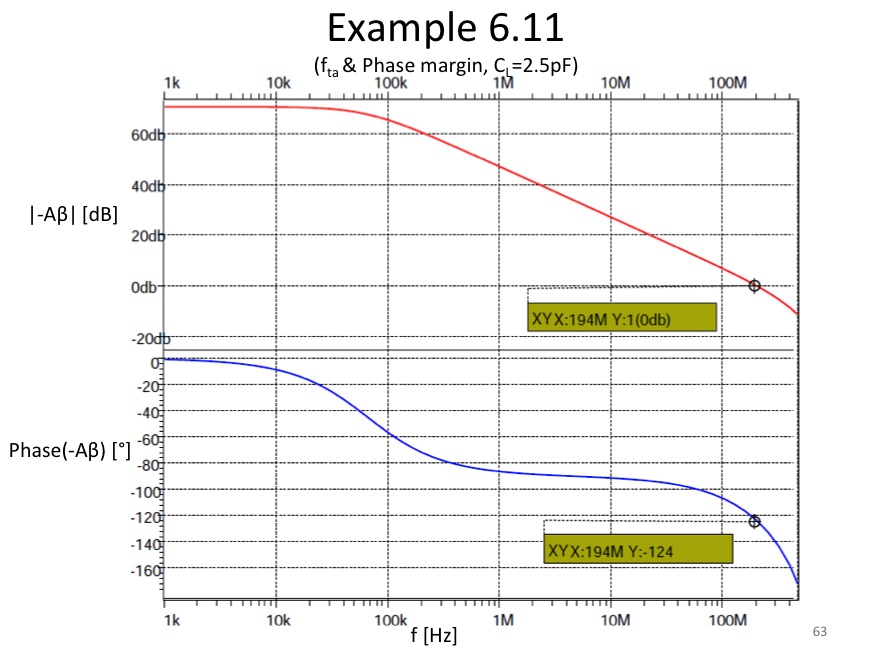

1-3. Simulation Result

fta = 194 MHz (CL = 2.5pF)

Phase margin = 56degrees

fta = 104 MHz (CL = 5pF)

Phase margin = 71degrees

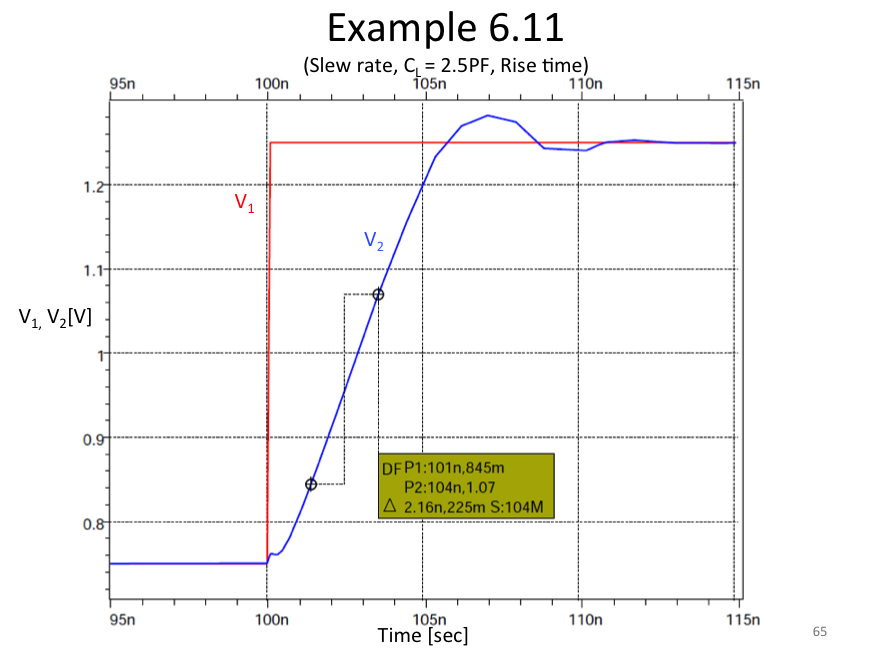

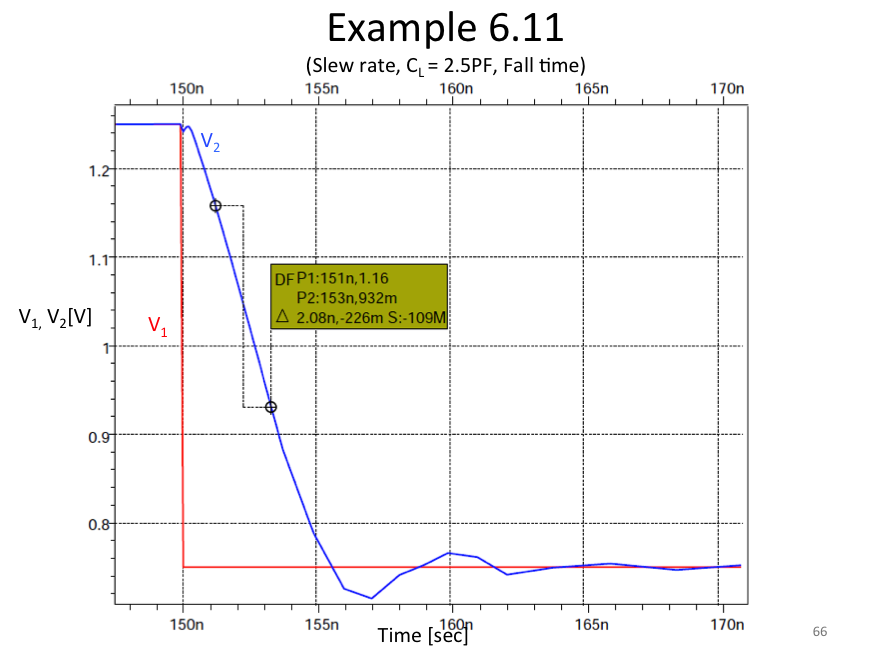

2. Slew rate

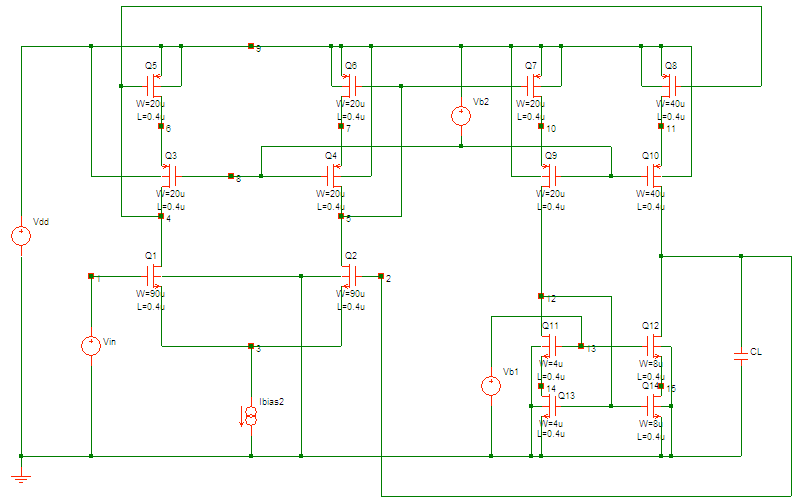

2-1. Schematic

2-2. HSPICE Netlist

* Example 6.11 for Slew rate

* MOS model

.include p18_cmos_models_tt.inc

* main circuit (Current-mirror opamp)

* input stage

m1 4 1 3 0 nmos w=90u l=0.4u

m2 5 2 3 0 nmos w=90u l=0.4u

m3 4 8 6 9 pmos w=40u l=0.4u

m4 5 8 7 9 pmos w=40u l=0.4u

m5 6 4 9 9 pmos w=20u l=0.4u

m6 7 5 9 9 pmos w=20u l=0.4u

*output stage

m7 10 5 9 9 pmos w=20u l=0.4u

m8 11 4 9 9 pmos w=40u l=0.4u

m9 12 8 10 9 pmos w=20u l=0.4u

m10 2 8 11 9 pmos w=40u l=0.4u

m11 12 13 14 0 nmos w=4u l=0.4u

m12 2 13 15 0 nmos w=8u l=0.4u

m13 14 12 0 0 nmos w=4u l=0.4u

m14 15 12 0 0 nmos w=8u l=0.4u

*load capacitance

cl 2 0 2.5p

* current source

Ibias 3 0 160u

* voltage source

Vdd 9 0 1.8

Vin 1 0 1 pulse(0.75 1.25 0 0.1n 0.1n 49.8n 100n)

Vb1 13 0 1.4

Vb2 9 8 1.2

* analysis

.op

.tran 1n 300n

* options

.options post

.end

2-3. Simulation Result

Slew rate = 104V/µs