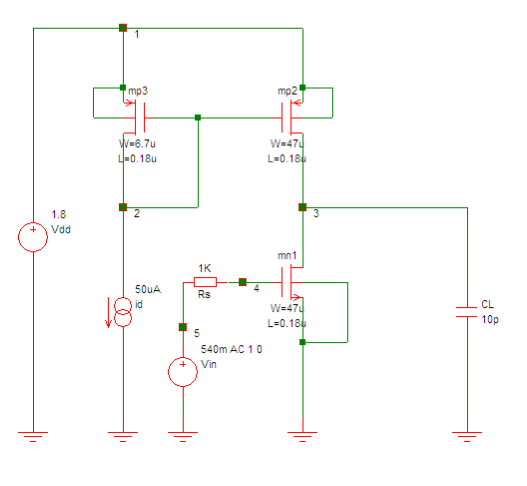

Example 4.12

1. Schematic

2. HSPICE Netlist

* Example 4.12

* MOS model

.include p18_cmos_models_tt.inc

* main circuit

mn1 3 4 0 0 nmos L=0.18u W=47u

mp2 3 2 1 1 pmos L=0.18u W=47u

mp3 2 2 1 1 pmos L=0.18u W=6.7u

rs 4 5 1k

cl 3 0 10p

* current source

id 2 0 dc 50u

* voltage source

Vdd 1 0 dc 1.8

vin 5 0 dc 0.54 ac 1

** vin dc value adjusted to ensure mn1 is in active mode

* analysis

.op

.ac dec 10 1k 100G

* options

.options post

.end

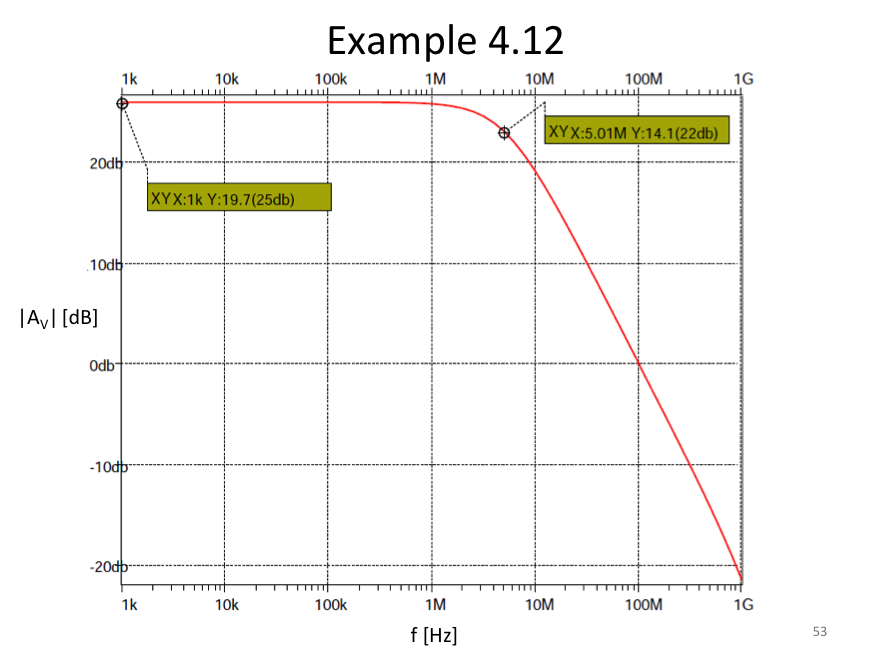

3. Simulation Result

| AV [V/V] | P [mW] | ω-3dB [MHz] | |

| Specifications | ≥20 | minimum | 5 |

| Simulation results | 19.7 | 0.83 | 5.0 |