Problem 7.1

a.

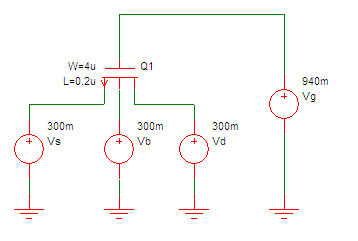

a-1. Schematic

a-2. HSPICE Netlist

* Problem 7.1 a.

* MOS model

.include p18_cmos_models_tt.inc

*main circuit

m1 Q1_D Q1_G Q1_S Q1_B nmos L=0.2u W=4u

* voltage source

Vg Q1_G 0 0.935

Vd Q1_D 0 0.3

Vs Q1_S 0 0.3

Vb Q1_B 0 0.3

* analysis

.op

* options

.options post

.end

a-3. Simulation Result

rds = 1.1kΩ

b.

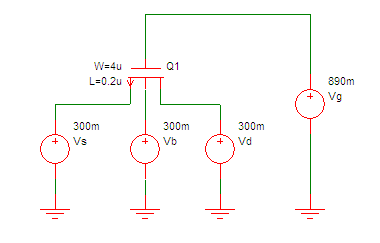

b-1. Schematic

b-2. HSPICE Netlist

* Problem 7.1 b.

* MOS model

.include p18_cmos_models_tt.inc

*main circuit

m1 Q1_D Q1_G Q1_S Q1_B nmos L=0.2u W=4u mulu0=1.3

* voltage source

Vg Q1_G 0 0.892

Vd Q1_D 0 0.3

Vs Q1_S 0 0.3

Vb Q1_B 0 0.3

* analysis

.op

* options

.options post

.end

b-3. Simulation Result

rds = 1.2kΩ