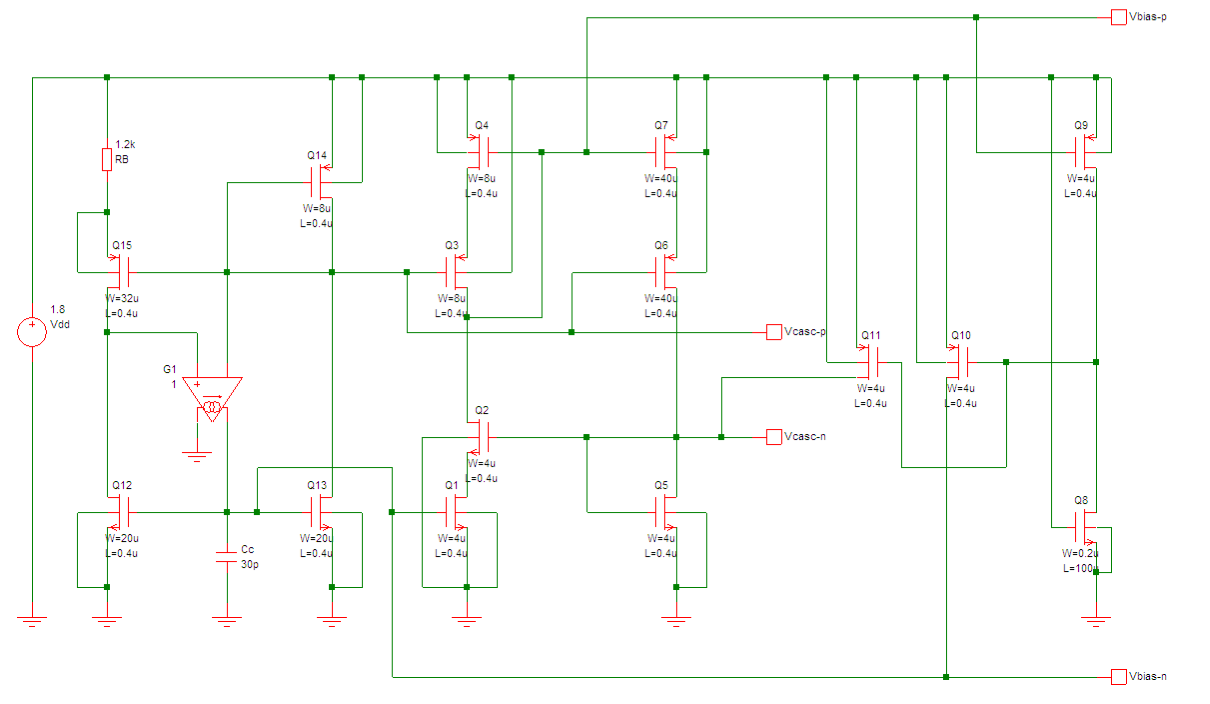

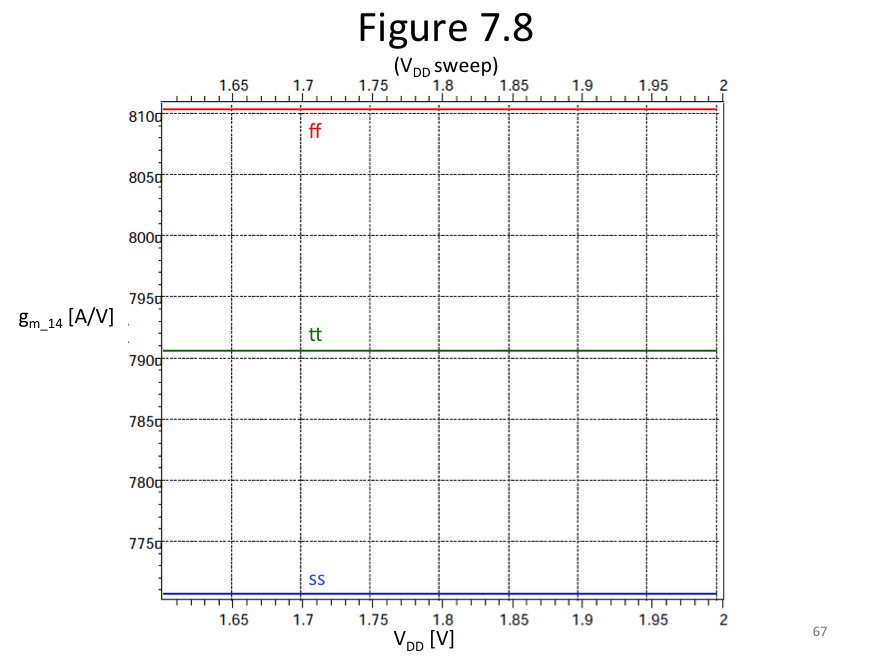

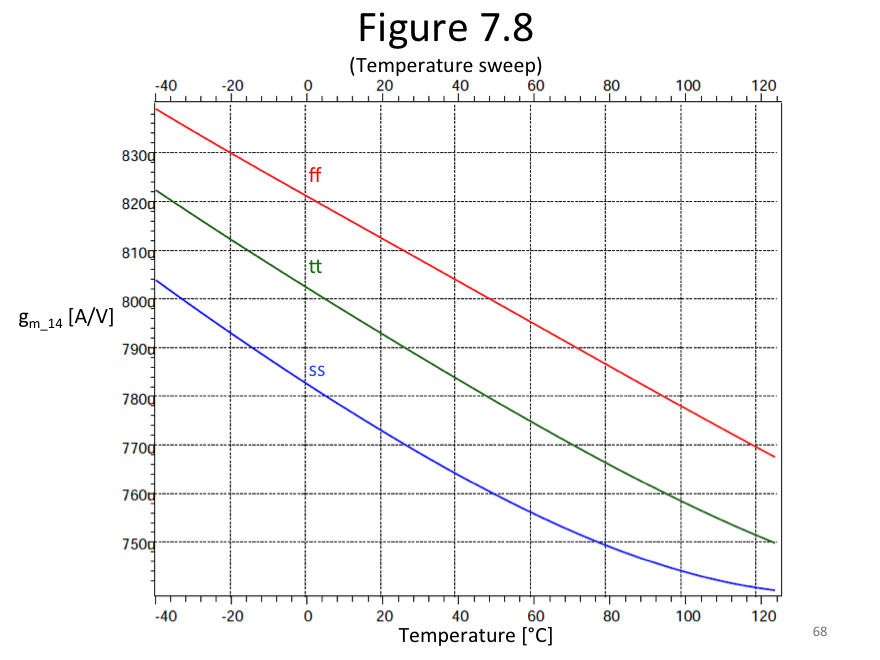

Figure 7.8

1. Schematic

2. HSPICE Netlist

* Section 7.2.2 Improved Constant Transconductance Circuit

* MOS model

.include p18_cmos_models_tt.inc

*.include p18_cmos_models_ss.inc

*.include p18_cmos_models_ff.inc

*main circuit (constant gm maclaren style)

*bias loop

m12 m15_D Vbias-n 0 0 nmos L=0.2u W=20u

m13 Vcasc-p Vbias-n 0 0 nmos L=0.2u W=20u

m14 Vcasc-p Vcasc-p Vdd_P Vdd_P pmos L=0.2u W=8u

m15 m15_D Vcasc-p RB_N RB_N pmos L=0.2u W=32u

RB Vdd_P RB_N 1.2k

G1 0 Vbias-n m15_D Vcasc-p 1

Cc Vbias-n 0 30p

*cascode bias

m1 m2_S Vbias-n 0 0 nmos L=0.2u W=4u

m2 Vbias-p Vcasc-n m2_S 0 nmos L=0.2u W=4u

m3 Vbias-p Vcasc-p m4_D Vdd_P pmos L=0.2u W=8u

m4 m4_D Vbias-p Vdd_P Vdd_P pmos L=0.2u W=8u

m5 Vcasc-n Vcasc-n 0 0 nmos L=0.2u W=4u

m6 Vcasc-n Vcasc-p m7_D Vdd_P pmos L=0.2u W=40u

m7 m7_D Vbias-p Vdd_P Vdd_P pmos L=0.2u W=40u

*start-up circuit

m8 m9_D Vdd_P 0 0 nmos L=100u W=0.2u

m9 m9_D Vbias-p Vdd_P Vdd_P pmos L=0.2u W=4u

m10 Vbias-n m9_D Vdd_P Vdd_P pmos L=0.2u W=4u

m11 Vcasc-n m9_D Vdd_P Vdd_P pmos L=0.2u W=4u

* voltage source

Vdd Vdd_P 0 1.8

* analysis

.op

.dc Vdd 1.6 2 10m

.dc temp -50 100 5

* options

.options post

.print lx7(m14) lx7(m13) lx7(m4)

.end