Problem 4.12

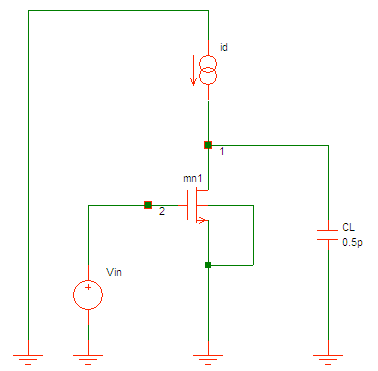

1. Schematic

2. HSPICE Netlist

2-a. 0.18µm CMOS process

* Problem 4.12 for 0.18um process

* MOS model

.include p18_cmos_models_tt.inc

* main circuit

mn1 1 2 0 0 nmos L=0.18u W=10u

cl 1 0 0.5p

* current source

id 0 1 dc 75u

* voltage source

vin 2 0 dc 0.55 ac 1

** vin dc value adjusted to ensure mn1 is in active mode

* analysis

.op

.ac dec 10 1k 100G

* options

.options post

.end

2-b. 45-nm CMOS process

* Problem 4.12 for 45nm process

* MOS model

.include p045_cmos_models_tt.inc

* main circuit

mn1 1 2 0 0 nmos L=45n W=643n

cl 1 0 0.5p

* current source

id 0 1 dc 20u

* voltage source

vin 2 0 dc 0.55 ac 1

** vin dc value adjusted to ensure mn1 is in active mode

* analysis

.op

.ac dec 10 1k 100G

* options

.options post

.end

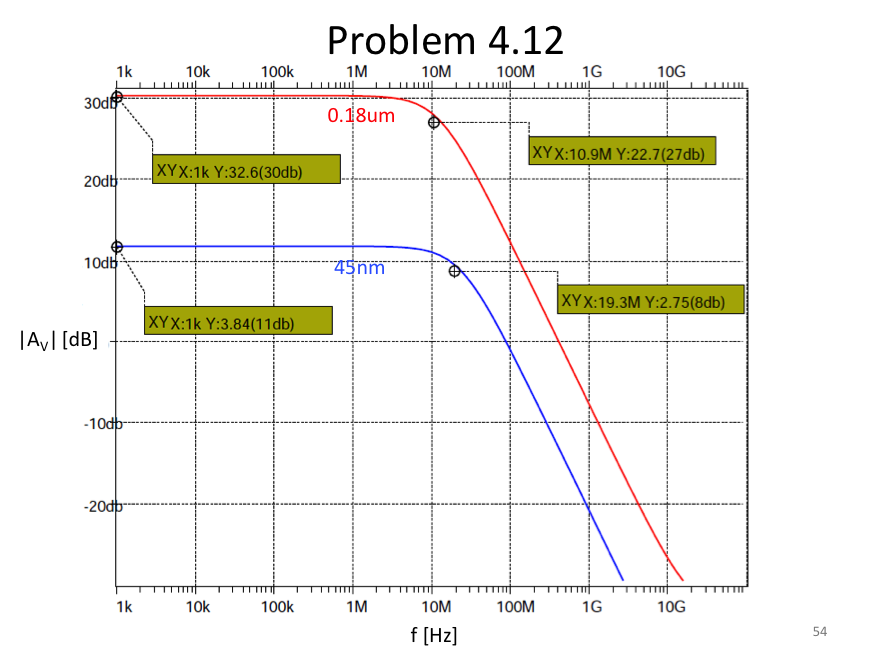

3. Simulation Result

| AV [V/V] | ω-3dB [MHz] | |

| Specifications | maximum | ≥10 |

| 0.18µm process | 32.6 | 10.9 |

| 45nm process | 3.84 | 19.3 |