Problem 10.10

1. Input offset voltage

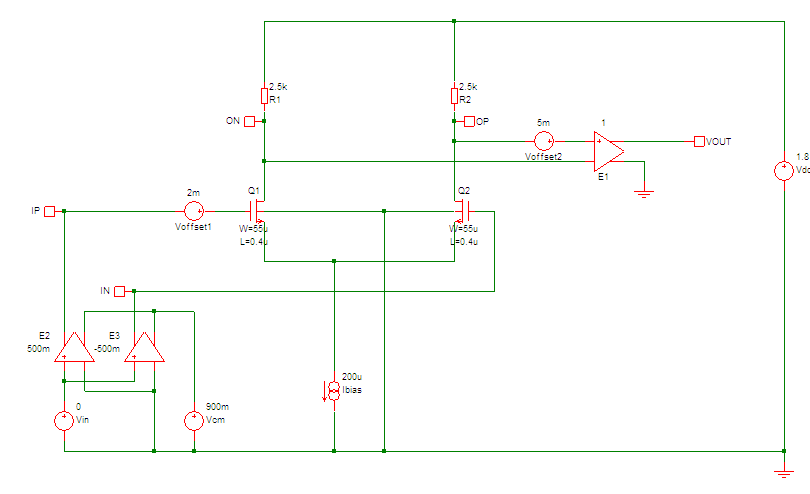

1-1. Schematic

1-2. HSPICE Netlist

* Problem 10.10 input offset voltage

* MOS model

.include p18_cmos_models_tt.inc

*pre-amplifier

r1 R1_P ON 2.5k

r2 R1_P OP 2.5k

m1 ON Voffset1_P Q1_S 0 nmos L=0.4u W=55u

m2 OP IN Q1_S 0 nmos L=0.4u W=55u

Ibias Q1_S 0 200u

*positive-feedback latch

E1 VOUT 0 Voffset2_P ON 1

* voltage source

Voffset1 Voffset1_P IP 2m

Voffset2 Voffset2_P OP 5m

Vdd R1_P 0 1.8

Vin E2_CP 0 0

Vcm E2_N 0 900m

E2 IP E2_N E2_CP 0 0.5

E3 IN E2_N E2_CP 0 -0.5

* analysis

.op

.dc Vin -10m 10m 1u

* options

.options post

.end

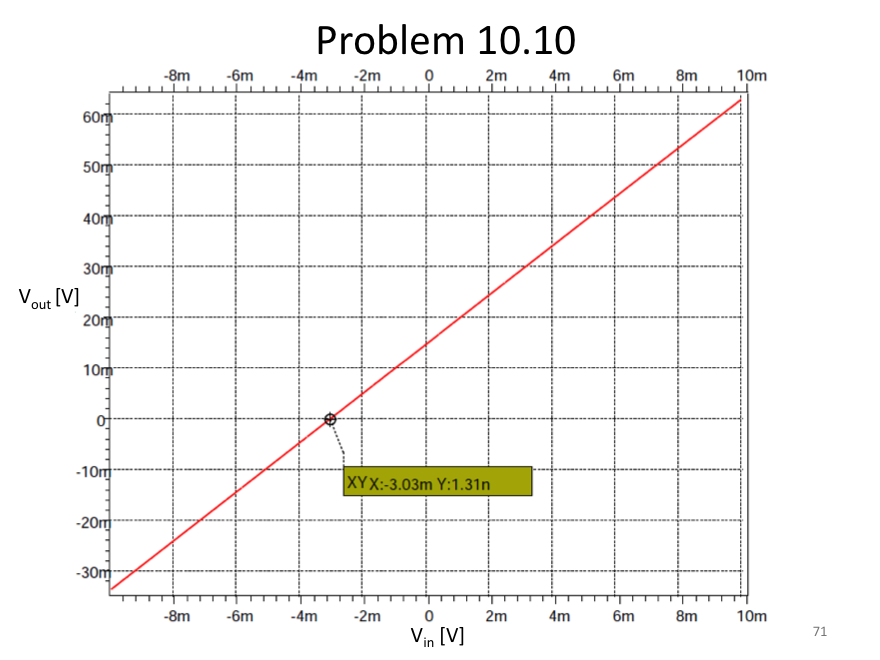

1-3. Simulation Result

Voff_total = 3.0mV with Voff_preamp = 2mV and Voff_latch = 5mV

2. Input noise

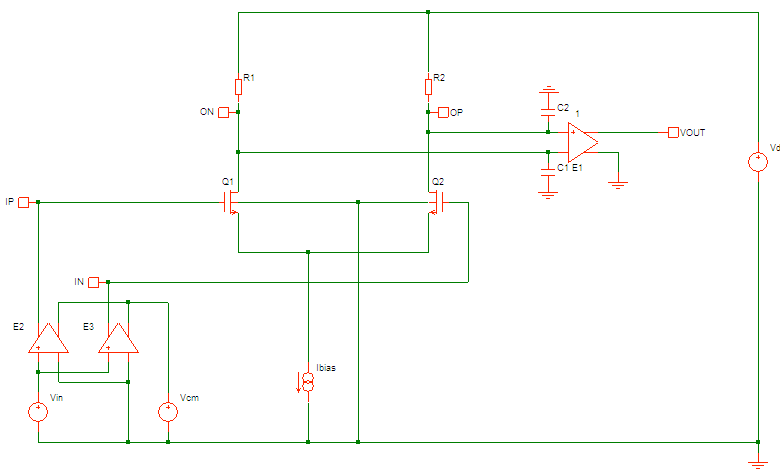

2-1. Schematic

2-2. HSPICE Netlist

* Problem 10.10 input noise

* MOS model

.include p18_cmos_models_tt.inc

*pre-amplifier

r1 R1_P ON 2.5k

r2 R1_P OP 2.5k

m1 ON IP Q1_S 0 nmos L=0.4u W=55u

m2 OP IN Q1_S 0 nmos L=0.4u W=55u

Ibias Q1_S 0 200u

*positive-feedback latch

E1 VOUT 0 OP ON 1

C1 ON 0 100f

C2 OP 0 100f

* voltage source

Vdd R1_P 0 1.8

Vin E2_CP 0 dc 0 ac 1

Vcm E2_N 0 900m

E2 IP E2_N E2_CP 0 0.5

E3 IN E2_N E2_CP 0 -0.5

* analysis

.op

.ac dec 10 1k 1T

.noise V(VOUT) Vin 10

* options

.options post

.print noise inoise

.end

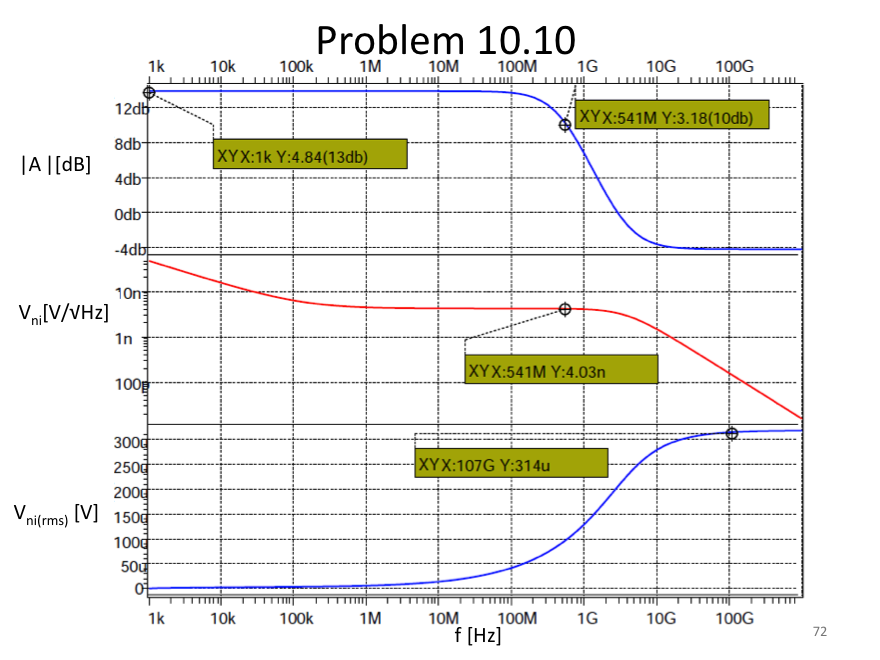

2-3. Simulation Result

Vni(rms) = 0.314mV