Problem 14.3

1. 0.18um CMOS process

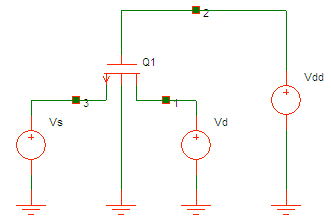

1-1. Schematic

1-2. HSPICE Netlist

* Problem 14.3 for 18um process

* MOS model

.include p18_cmos_models_tt.inc

*main circuit (nmos switch)

m1 1 2 3 0 nmos L=0.22u W=0.36u

* voltage source

Vdd 2 0 1.8

Vd 1 0 0.9

Vs 3 0 0.9

* analysis

.op

* options

.options post

.end

1-3. Simulation Result

| RON [kΩ] at Vg = Vdd |

Cg [fF] |

| 6.52 | 0.97 |

2. 45nm CMOS process

2-1. Schematic

2-2. HSPICE Netlist

* Problem 14.3 for 45nm process

* MOS model

.include p045_cmos_models_tt.inc

*main circuit (nmos switch)

m1 1 2 3 0 nmos L=45n W=0.6u

* voltage source

Vdd 2 0 1

Vd 1 0 0.5

Vs 3 0 0.5

* analysis

.op

* options

.options post

.end

2-3. Simulation Result

| RON [kΩ] at Vg = Vdd |

Cg [fF] |

| 7.81 | 0.627 |