Problem 3.3

a. Threshold voltage

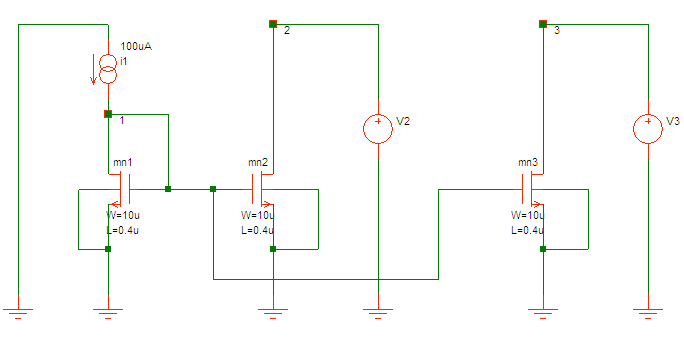

a-1. Schematic

a-2. HSPICE Netlist

* Problem 3.3 a.

* MOS model

.include p35_cmos_models_tt.inc

* main circuit

mn1 1 1 0 0 nmos L=0.4u W=10u

mn2 2 1 0 0 nmos L=0.4u W=10u

mn3 3 1 0 0 nmos L=0.4u W=10u delvto=5m

* current source

i1 0 1 100u

* voltage source

v2 2 0 1

V3 3 0 1

* analysis

.op

* options

.options post

.end

a-3. Simulation Result

| Variation | Iout [µA] | ΔIout [%] |

| Typical | 104.7 | 0 |

| Vtn: +5mV | 99.7 | -4.8 |

b.Carrier mobility

b-1. Schematic

b-2. HSPICE Netlist

* Problem 3.3 b.

* MOS model

.include p35_cmos_models_tt.inc

* main circuit

mn1 1 1 0 0 nmos L=0.4u W=10u

mn2 2 1 0 0 nmos L=0.4u W=10u

mn3 3 1 0 0 nmos L=0.4u W=10u mulu0=1.05

* current source

i1 0 1 100u

* voltage source

v2 2 0 1

V3 3 0 1

* analysis

.op

* options

.options post

.end

b-3. Simulation Result

| Variation | Iout [µA] | ΔIout [%] |

| Typical | 104.7 | 0 |

| μn: +5% | 109.3 | 4.4 |

c. Gate length

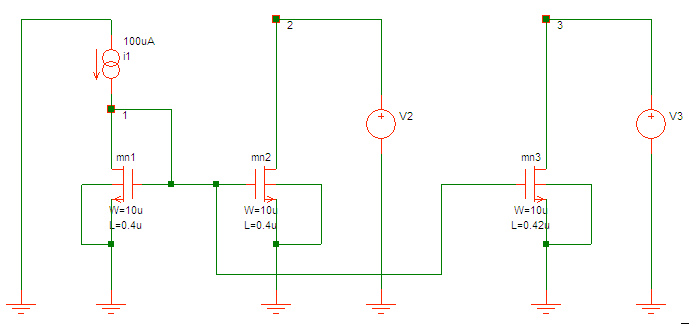

c-1. Schematic

c-2. HSPICE Netlist* Problem 3.3 c.

* MOS model

.include p35_cmos_models_tt.inc

* main circuit

mn1 1 1 0 0 nmos L=0.4u W=10u

mn2 2 1 0 0 nmos L=0.4u W=10u

mn3 3 1 0 0 nmos L=0.42u W=10u

* current source

i1 0 1 100u

* voltage source

v2 2 0 1

V3 3 0 1

* analysis

.op

* options

.options post

.end

c-3. Simulation Result

| Variation | Iout [µA] | ΔIout [%] |

| Typical | 104.7 | 0 |

| L: +5% | 94.9 | -9.4 |